基于KC705 開發(fā)板 的FPGA ethernet 實(shí)際完整項(xiàng)目(代碼)可定制修改

4

4

拍明

拍明

原標(biāo)題:基于KC705 開發(fā)板 的FPGA ethernet 實(shí)際完整項(xiàng)目(代碼)可定制修改

一、項(xiàng)目概述

本項(xiàng)目基于 Xilinx KC705 開發(fā)板,其搭載了 Xilinx Virtex-7 FPGA 芯片,具有高速串行收發(fā)器、大容量存儲(chǔ)資源和豐富的 IO 接口。利用開發(fā)板上原生支持的高速串口、DDR3 SDRAM、以及板載的時(shí)鐘資源,設(shè)計(jì)一套完整的 FPGA Ethernet 通信方案,實(shí)現(xiàn)數(shù)據(jù)的高速傳輸和網(wǎng)絡(luò)協(xié)議處理。項(xiàng)目中采用基于 FPGA 實(shí)現(xiàn)的 Ethernet MAC/IP 核,通過(guò)高速以太網(wǎng)接口與上位機(jī)或其他網(wǎng)絡(luò)設(shè)備通信,同時(shí)支持用戶自定義數(shù)據(jù)處理邏輯。該方案具備高度定制化的特性,能夠根據(jù)實(shí)際應(yīng)用需要靈活修改數(shù)據(jù)協(xié)議、增加功能模塊,實(shí)現(xiàn)實(shí)時(shí)數(shù)據(jù)采集、處理及傳輸。

二、系統(tǒng)架構(gòu)設(shè)計(jì)

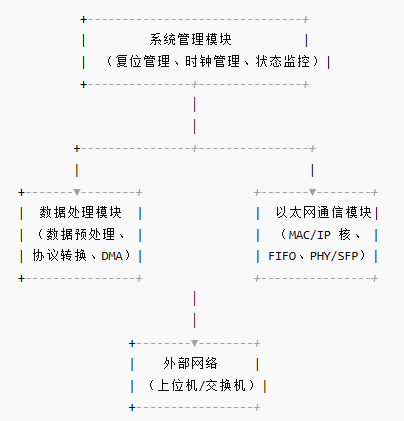

本項(xiàng)目系統(tǒng)主要分為三大部分:以太網(wǎng)通信模塊、數(shù)據(jù)處理模塊以及系統(tǒng)管理模塊。

以太網(wǎng)通信模塊:

利用 FPGA 內(nèi)部邏輯實(shí)現(xiàn) Ethernet MAC 核,負(fù)責(zé)對(duì)以太網(wǎng)幀進(jìn)行封裝和解析,并與外部 PHY 或 SFP 模塊進(jìn)行物理層交互。該模塊支持全雙工傳輸,能夠?qū)崿F(xiàn)高速數(shù)據(jù)通信,并通過(guò) DMA 方式與外部存儲(chǔ)器進(jìn)行數(shù)據(jù)交互。為滿足實(shí)時(shí)傳輸要求,本模塊設(shè)計(jì)了高效的 FIFO 緩沖機(jī)制,確保數(shù)據(jù)流在發(fā)送與接收過(guò)程中的穩(wěn)定性和完整性。數(shù)據(jù)處理模塊:

數(shù)據(jù)處理模塊主要包括數(shù)據(jù)預(yù)處理、數(shù)據(jù)協(xié)議轉(zhuǎn)換以及數(shù)據(jù)存儲(chǔ)控制等子模塊。該模塊利用 FPGA 并行處理能力,實(shí)現(xiàn)數(shù)據(jù)的高速采集、過(guò)濾和存儲(chǔ)。根據(jù)用戶需求,可以靈活定制數(shù)據(jù)處理算法,例如對(duì)數(shù)據(jù)進(jìn)行CRC 校驗(yàn)、數(shù)據(jù)加密或協(xié)議轉(zhuǎn)換。模塊內(nèi)部設(shè)計(jì)采用流水線和并行處理技術(shù),確保在高速數(shù)據(jù)傳輸環(huán)境下仍能實(shí)時(shí)響應(yīng)。系統(tǒng)管理模塊:

系統(tǒng)管理模塊負(fù)責(zé)整個(gè)系統(tǒng)的時(shí)鐘管理、復(fù)位管理、狀態(tài)監(jiān)控以及與上位機(jī)的通信接口。采用狀態(tài)機(jī)設(shè)計(jì)實(shí)現(xiàn)各個(gè)模塊間的協(xié)調(diào)工作,并通過(guò)配置寄存器對(duì)整個(gè)系統(tǒng)的工作參數(shù)進(jìn)行調(diào)整。系統(tǒng)管理模塊還負(fù)責(zé)監(jiān)控系統(tǒng)運(yùn)行狀態(tài),提供錯(cuò)誤檢測(cè)和異常處理機(jī)制,保證系統(tǒng)在異常情況下能夠安全恢復(fù)。

整個(gè)系統(tǒng)架構(gòu)的設(shè)計(jì)如圖所示:

三、優(yōu)選元器件及器件說(shuō)明

在本項(xiàng)目中,為確保系統(tǒng)實(shí)現(xiàn)穩(wěn)定、高速的通信及數(shù)據(jù)處理功能,所有元器件的選擇均經(jīng)過(guò)嚴(yán)格評(píng)估和比對(duì)。下面詳細(xì)說(shuō)明每個(gè)主要元器件的型號(hào)、作用、選擇依據(jù)以及功能描述。

FPGA 主控芯片:Xilinx Virtex-7 XC7VX485T

器件作用:作為整個(gè)系統(tǒng)的核心處理單元,負(fù)責(zé)實(shí)現(xiàn)所有數(shù)字邏輯電路、數(shù)據(jù)處理和通信協(xié)議。

選擇依據(jù):Virtex-7 系列擁有強(qiáng)大的 DSP 資源和高速串行收發(fā)器,支持多千兆位以太網(wǎng)接口;具備較高的邏輯密度和豐富的內(nèi)嵌資源,非常適合實(shí)現(xiàn)復(fù)雜的實(shí)時(shí)數(shù)據(jù)處理和高速網(wǎng)絡(luò)通信。

功能描述:支持并行計(jì)算、數(shù)據(jù)加速、實(shí)時(shí)信號(hào)處理以及內(nèi)嵌 IP 核的無(wú)縫集成,能夠通過(guò)硬件加速實(shí)現(xiàn)數(shù)據(jù)封裝、解析、存儲(chǔ)和傳輸?shù)裙δ堋?/span>

時(shí)鐘源:低抖動(dòng)高速時(shí)鐘振蕩器(型號(hào):SiTime SiT9082)

器件作用:提供系統(tǒng)主時(shí)鐘信號(hào),確保 FPGA 內(nèi)部所有邏輯模塊同步工作。

選擇依據(jù):SiTime 系列產(chǎn)品具有低相位噪聲、穩(wěn)定性高的特點(diǎn),能夠提供精準(zhǔn)的時(shí)鐘源,確保高速數(shù)據(jù)傳輸過(guò)程中時(shí)鐘抖動(dòng)不影響信號(hào)完整性。

功能描述:為所有高速串行接口和內(nèi)部邏輯提供參考時(shí)鐘,同時(shí)支持溫度補(bǔ)償功能,保證在不同環(huán)境下時(shí)鐘頻率穩(wěn)定。

存儲(chǔ)器:DDR3 SDRAM(型號(hào):Micron MT41J128M16HA-125)

器件作用:作為數(shù)據(jù)緩存和臨時(shí)存儲(chǔ)區(qū),主要用于以太網(wǎng)數(shù)據(jù)幀的緩沖、存儲(chǔ)和快速交換。

選擇依據(jù):DDR3 SDRAM 具有高帶寬、低延遲和較大容量,能夠滿足實(shí)時(shí)數(shù)據(jù)傳輸過(guò)程中對(duì)高速數(shù)據(jù)緩存的要求,同時(shí)支持 FPGA 內(nèi)部 DMA 直接訪問(wèn),提高數(shù)據(jù)處理效率。

功能描述:主要用于存儲(chǔ)接收到的以太網(wǎng)幀數(shù)據(jù)及用戶處理后的數(shù)據(jù),確保系統(tǒng)在高數(shù)據(jù)速率下不會(huì)出現(xiàn)數(shù)據(jù)丟失現(xiàn)象。

網(wǎng)絡(luò)物理層模塊:SFP 模塊(型號(hào):Finisar FTLF8524P2BNL)

器件作用:提供光纖通信接口,將 FPGA 內(nèi)部的電信號(hào)轉(zhuǎn)換為適合光纖傳輸?shù)墓庑盘?hào),實(shí)現(xiàn)遠(yuǎn)距離、高速的數(shù)據(jù)通信。

選擇依據(jù):該型號(hào) SFP 模塊支持千兆以太網(wǎng)通信,傳輸速率穩(wěn)定且抗干擾能力強(qiáng),非常適合工業(yè)環(huán)境中要求高可靠性和高速傳輸?shù)膽?yīng)用。

功能描述:實(shí)現(xiàn) FPGA 與外部光纖網(wǎng)絡(luò)的互聯(lián),支持熱插拔和多種傳輸模式,是整個(gè)以太網(wǎng)通信鏈路中的關(guān)鍵器件。

高速以太網(wǎng) PHY 芯片:Analog Devices ADIN2111

器件作用:作為網(wǎng)絡(luò)物理層接口,實(shí)現(xiàn)數(shù)據(jù)的串行傳輸和接收,將數(shù)字信號(hào)轉(zhuǎn)換為物理信號(hào)。

選擇依據(jù):ADIN2111 具有高集成度、低功耗和高速傳輸能力,支持全雙工通信和自動(dòng)協(xié)商功能,非常適合與 FPGA 內(nèi)部 MAC 核配合使用。

功能描述:提供信號(hào)編碼、調(diào)制、解調(diào)以及信號(hào)完整性保護(hù)功能,同時(shí)具備自適應(yīng)均衡和誤碼檢測(cè)功能,確保通信鏈路的高可靠性。

電源管理模塊:DC-DC 轉(zhuǎn)換器(型號(hào):TI TPS54560)

器件作用:為整個(gè)系統(tǒng)提供穩(wěn)定的多路電源,確保 FPGA 及其他外圍器件的正常供電。

選擇依據(jù):TPS54560 具有高效率、寬輸入電壓范圍和低紋波噪聲特性,適合用于高頻率高速系統(tǒng)中對(duì)電源質(zhì)量要求較高的場(chǎng)合。

功能描述:能夠?qū)⑤斎胫绷麟妷恨D(zhuǎn)換為系統(tǒng)所需的各個(gè)電壓等級(jí),同時(shí)提供多路輸出,保證各個(gè)模塊在不同電壓下均能穩(wěn)定運(yùn)行。

配置及通信接口:USB-to-UART 模塊(型號(hào):FTDI FT2232H)

器件作用:實(shí)現(xiàn) FPGA 與上位機(jī)之間的串行通信,便于系統(tǒng)調(diào)試、配置和數(shù)據(jù)傳輸。

選擇依據(jù):FT2232H 提供高速 USB 通信接口,支持多種串行通信協(xié)議,且軟件驅(qū)動(dòng)成熟、使用方便,非常適合原型開發(fā)階段調(diào)試及數(shù)據(jù)傳輸。

功能描述:作為調(diào)試接口,將系統(tǒng)狀態(tài)、錯(cuò)誤信息和調(diào)試數(shù)據(jù)傳輸?shù)缴衔粰C(jī),并支持在線配置和調(diào)試。

輔助器件:電容、電感、濾波器等

器件作用:提供信號(hào)濾波、去耦及電源穩(wěn)定性支持,確保各模塊信號(hào)質(zhì)量。

選擇依據(jù):選用高精度低 ESR 的陶瓷電容、低直流電阻電感器以及高效濾波器件,確保在高速數(shù)據(jù)傳輸過(guò)程中信號(hào)無(wú)干擾和電源噪聲極小。

功能描述:保護(hù)高速信號(hào)和電源線,減少因噪聲引起的信號(hào)畸變和系統(tǒng)誤判,確保整體系統(tǒng)的可靠運(yùn)行。

四、系統(tǒng)電路框圖說(shuō)明

本方案在硬件設(shè)計(jì)上采用分層模塊化設(shè)計(jì),主要模塊之間通過(guò)標(biāo)準(zhǔn)信號(hào)總線和控制接口連接。下面對(duì)電路框圖進(jìn)行詳細(xì)說(shuō)明。

在該電路框圖中,F(xiàn)PGA 作為整個(gè)系統(tǒng)的核心,通過(guò)高速互聯(lián)與 DDR3 SDRAM 以及以太網(wǎng)模塊相連接。DDR3 用于緩存高速數(shù)據(jù)流,而以太網(wǎng) MAC/IP 核通過(guò)內(nèi)部邏輯實(shí)現(xiàn)數(shù)據(jù)的封裝和解析,最終通過(guò)網(wǎng)絡(luò) PHY 或 SFP 模塊實(shí)現(xiàn)與外部網(wǎng)絡(luò)設(shè)備的通信。同時(shí),電源管理模塊為整個(gè)系統(tǒng)提供穩(wěn)定、低噪聲的多路電源,確保各個(gè)器件穩(wěn)定運(yùn)行。

五、FPGA 代碼實(shí)現(xiàn)及模塊劃分

在 FPGA 內(nèi)部設(shè)計(jì)中,主要采用 Verilog HDL 實(shí)現(xiàn)各個(gè)模塊,整個(gè)設(shè)計(jì)分為以下幾個(gè)主要模塊:

Ethernet MAC 模塊

采用標(biāo)準(zhǔn)的 10/100/1000 Mbps Ethernet MAC 協(xié)議,通過(guò) FIFO 緩沖與數(shù)據(jù)處理模塊進(jìn)行數(shù)據(jù)交換。內(nèi)部包含幀定界、地址匹配、CRC 校驗(yàn)以及 DMA 接口控制,支持多種傳輸模式。

核心代碼示例如下:

module ethernet_mac (

input clk,

input rst_n,

// 接收數(shù)據(jù)接口

input [7:0] rx_data,

input rx_valid,

output reg rx_ready,

// 發(fā)送數(shù)據(jù)接口

output reg [7:0] tx_data,

output reg tx_valid,

input tx_ready,

// DMA 接口

output reg [31:0] dma_wr_data,

output reg dma_wr_en,

input dma_wr_ready,

// 狀態(tài)監(jiān)控

output reg link_status

);

// 內(nèi)部狀態(tài)定義

reg [15:0] rx_frame_len;

reg [31:0] crc_reg;

reg [2:0] state;

localparam STATE_IDLE = 3'd0,

STATE_RECEIVE = 3'd1,

STATE_CHECK_CRC= 3'd2,

STATE_SEND = 3'd3,

STATE_DMA = 3'd4;

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

state <= STATE_IDLE;

rx_ready <= 1'b0;

tx_valid <= 1'b0;

dma_wr_en <= 1'b0;

rx_frame_len <= 16'd0;

crc_reg <= 32'hFFFFFFFF;

link_status <= 1'b0;

end

else begin

case(state)

STATE_IDLE: begin

rx_ready <= 1'b1;

if(rx_valid) begin

rx_frame_len <= 16'd0;

crc_reg <= 32'hFFFFFFFF;

state <= STATE_RECEIVE;

end

end

STATE_RECEIVE: begin

if(rx_valid) begin

// 接收數(shù)據(jù),更新幀長(zhǎng)度及 CRC 校驗(yàn)

rx_frame_len <= rx_frame_len + 1;

crc_reg <= crc_update(crc_reg, rx_data);

if(rx_frame_len == 16'd1518) begin

state <= STATE_CHECK_CRC;

end

end

else if(!rx_valid && rx_frame_len > 16'd0) begin

state <= STATE_CHECK_CRC;

end

end

STATE_CHECK_CRC: begin

// 簡(jiǎn)單CRC檢查示例

if(crc_reg == 32'hDEBB20E3) begin

state <= STATE_DMA;

end

else begin

state <= STATE_IDLE;

end

end

STATE_DMA: begin

if(dma_wr_ready) begin

dma_wr_data <= {24'd0, rx_data}; // 簡(jiǎn)單示例

dma_wr_en <= 1'b1;

state <= STATE_SEND;

end

end

STATE_SEND: begin

if(tx_ready) begin

tx_data <= rx_data;

tx_valid <= 1'b1;

state <= STATE_IDLE;

end

end

default: state <= STATE_IDLE;

endcase

end

end

// CRC 更新函數(shù)(偽代碼)

function [31:0] crc_update;

input [31:0] current_crc;

input [7:0] data_byte;

begin

crc_update = current_crc ^ {data_byte, 24'd0}; // 示例實(shí)現(xiàn),實(shí)際應(yīng)用中應(yīng)使用標(biāo)準(zhǔn) CRC 算法

end

endfunction

endmodule

DMA 數(shù)據(jù)傳輸模塊

該模塊負(fù)責(zé)在 FPGA 內(nèi)部與 DDR3 SDRAM 或其他存儲(chǔ)器之間傳輸數(shù)據(jù),采用雙緩沖技術(shù)與 FIFO 數(shù)據(jù)緩存,確保數(shù)據(jù)在高速傳輸時(shí)不會(huì)出現(xiàn)擁塞或丟失。代碼中通過(guò)握手信號(hào)(如 dma_wr_ready、dma_wr_en)實(shí)現(xiàn)數(shù)據(jù)傳輸控制,保證數(shù)據(jù)流的連續(xù)性。數(shù)據(jù)處理模塊

數(shù)據(jù)處理模塊主要包括數(shù)據(jù)預(yù)處理、地址匹配、數(shù)據(jù)包過(guò)濾等功能。利用 FPGA 的并行處理能力,完成數(shù)據(jù)的高速計(jì)算和轉(zhuǎn)換。該模塊內(nèi)部采用狀態(tài)機(jī)控制,保證數(shù)據(jù)流在各個(gè)子模塊間順利傳遞。系統(tǒng)管理模塊

實(shí)現(xiàn)系統(tǒng)時(shí)鐘復(fù)位、狀態(tài)監(jiān)控以及上位機(jī)調(diào)試接口。該模塊通過(guò) USB-to-UART 接口(FT2232H)與外部進(jìn)行通信,實(shí)現(xiàn)系統(tǒng)參數(shù)配置、狀態(tài)讀取及錯(cuò)誤處理。所有配置寄存器均通過(guò)狀態(tài)機(jī)動(dòng)態(tài)管理,便于后續(xù)功能擴(kuò)展。

六、軟件與固件開發(fā)

在 FPGA 端完成底層硬件邏輯實(shí)現(xiàn)后,項(xiàng)目還需要在上位機(jī)端開發(fā)軟件,用于系統(tǒng)配置、數(shù)據(jù)采集以及通信數(shù)據(jù)的展示。基于常見的開發(fā)環(huán)境,如 Xilinx Vivado 和 SDK,本項(xiàng)目軟件部分主要包含以下功能:

系統(tǒng)初始化與配置

軟件首先初始化 FPGA 系統(tǒng),下載配置文件(bitstream),并通過(guò)串口或網(wǎng)絡(luò)接口與 FPGA 進(jìn)行握手。初始化過(guò)程中讀取 FPGA 內(nèi)部寄存器狀態(tài),確保各模塊已正確啟動(dòng)。數(shù)據(jù)采集與監(jiān)控

利用 USB-to-UART 接口實(shí)現(xiàn)數(shù)據(jù)的實(shí)時(shí)采集,借助圖形化界面展示系統(tǒng)運(yùn)行狀態(tài)與數(shù)據(jù)傳輸情況。軟件中加入數(shù)據(jù)日志記錄、錯(cuò)誤報(bào)警等功能,便于系統(tǒng)調(diào)試和長(zhǎng)期監(jiān)控。定制化數(shù)據(jù)處理

根據(jù)用戶需求,軟件可以對(duì)接收到的數(shù)據(jù)進(jìn)行進(jìn)一步處理、分析或存儲(chǔ),并可通過(guò)協(xié)議轉(zhuǎn)換接口與其他系統(tǒng)交互。支持自定義插件式擴(kuò)展,滿足不同應(yīng)用場(chǎng)景的需求。

示例 C 語(yǔ)言代碼片段(基于 SDK 的串口通信)如下:

#include <stdio.h>

#include <stdlib.h>

#include "xuartps.h"

#include "platform.h"

#define UART_DEVICE_ID XPAR_XUARTPS_0_DEVICE_ID

XUartPs Uart_Ps;

int init_uart(void) {

XUartPs_Config *Config;

int Status;

Config = XUartPs_LookupConfig(UART_DEVICE_ID);

if (NULL == Config) {

return XST_FAILURE;

}

Status = XUartPs_CfgInitialize(&Uart_Ps, Config, Config->BaseAddress);

if (Status != XST_SUCCESS) {

return XST_FAILURE;

}

XUartPs_SetBaudRate(&Uart_Ps, 115200);

return XST_SUCCESS;

}

int main() {

int Status;

init_platform();

Status = init_uart();

if (Status != XST_SUCCESS) {

printf("UART 初始化失敗

");

return XST_FAILURE;

}

printf("FPGA Ethernet 系統(tǒng)啟動(dòng)成功

");

// 讀取 FPGA 數(shù)據(jù)寄存器示例

while (1) {

u8 Buffer[128];

int ReceivedCount = XUartPs_Recv(&Uart_Ps, Buffer, sizeof(Buffer));

if (ReceivedCount > 0) {

// 數(shù)據(jù)處理示例

Buffer[ReceivedCount] = '

產(chǎn)品分類

產(chǎn)品分類