74LS74 D型正邊觸發觸發器詳解

一、引言

74LS74是一個廣泛使用的D型正邊觸發觸發器(D Flip-Flop),屬于74系列集成電路中的一員。作為數字電路中重要的存儲元件,D型觸發器在數據存儲和狀態保持等多種應用中扮演著重要角色。本文將深入探討74LS74的常見型號、參數、工作原理、特點、作用和應用。

二、常見型號

74LS74系列有多個型號,以下是一些常見型號:

74LS74:標準D型觸發器,正邊觸發,具有兩個觸發器。

74HCT74:高電平兼容TTL的D型觸發器,適用于CMOS電路。

74HC74:高電平兼容的D型觸發器,適用于更廣泛的電壓范圍。

三、主要參數

在分析74LS74的性能時,以下是一些關鍵參數:

工作電壓:4.75V至5.25V(標準TTL電壓)

最大功耗:約為100mW

輸入電壓范圍:0V至5V(邏輯電平范圍)

輸出電流:最大可達20mA(每個輸出)

時鐘頻率:最大為30MHz(具體頻率取決于電路設計)

四、工作原理

4.1 D型觸發器的基本概念

D型觸發器是一個時序邏輯電路,其主要功能是將輸入的數據在特定時鐘信號的邊沿采樣并存儲。74LS74包含兩個相同的D觸發器,分別稱為D1和D2,通常可以獨立使用。

4.2 觸發器的工作原理

D型觸發器的工作過程如下:

輸入端:觸發器有一個D輸入(數據輸入),一個CLK輸入(時鐘輸入)和兩個輸出Q和Q'(反相輸出)。

時鐘信號:當時鐘信號的上升沿到達時,D輸入的狀態被鎖存到Q輸出。換句話說,D的狀態在時鐘上升沿時被“采樣”并保存。

保持狀態:一旦數據被鎖存,無論D輸入如何變化,Q輸出都會保持該狀態,直到下一個時鐘邊沿到來。

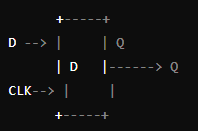

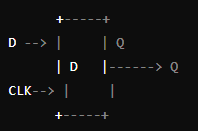

4.3 邏輯符號

D型觸發器的邏輯符號通常如下所示:

在時鐘信號CLK的上升沿,D的值被傳送到Q輸出。

五、特點

74LS74 D型觸發器具有以下顯著特點:

正邊觸發:觸發器僅在時鐘信號的上升沿有效,這有助于消除抖動和干擾帶來的錯誤。

雙觸發器結構:74LS74內部包含兩個獨立的D觸發器,可以同時進行數據存儲和處理。

高速:74LS系列具有較高的工作速度,適用于快速時序邏輯電路。

TTL兼容性:與其他TTL邏輯電路兼容,便于集成和使用。

六、作用

74LS74 D型觸發器在數字電路中起到以下幾方面的作用:

數據存儲:能夠存儲單比特數據,在數據處理和傳輸中起到緩沖作用。

狀態保持:用于保持電路的狀態,尤其在同步時序電路中。

數據鎖存:在需要將數據從一個時鐘周期轉移到另一個周期時,74LS74能夠在時鐘邊沿鎖存數據。

計數器和寄存器:可用于構建計數器、移位寄存器等更復雜的數字電路。

七、應用

74LS74 D型觸發器廣泛應用于各種數字電路中,主要包括:

時序電路:如計數器、分頻器等。

數據寄存器:用于存儲數據,特別是在微處理器和控制系統中。

狀態機設計:在有限狀態機(FSM)中用于狀態存儲和轉換。

同步數據傳輸:用于在多個邏輯電路之間同步數據傳輸。

7.1 時序電路

在時序電路中,74LS74 D型觸發器可以作為基本的存儲元件,結合其他邏輯門實現更復雜的功能。例如,在計數器電路中,多個D觸發器可連接在一起,實現對輸入脈沖的計數。

7.2 數據寄存器

74LS74可用于構建數據寄存器,用于在計算機中存儲和轉移數據。例如,在CPU中,D觸發器可以存儲操作數或指令,確保在特定時鐘周期內正確執行。

7.3 狀態機設計

在狀態機設計中,74LS74用于實現狀態的存儲和轉移。例如,在交通信號控制系統中,狀態機可以根據交通流量變化切換信號燈的狀態。

7.4 同步數據傳輸

在需要同步數據傳輸的系統中,74LS74 D型觸發器能夠確保數據在時鐘信號的控制下可靠地傳輸。例如,在數據總線的應用中,可以通過D觸發器實現數據的鎖存和傳送。

八、數字電路中不可或缺的基本元件

74LS74 D型正邊觸發觸發器是數字電路中不可或缺的基本元件,具有數據存儲、狀態保持、數據鎖存等多種功能。其雙觸發器設計、TTL兼容性和高速性能,使其在時序電路、數據寄存器、狀態機設計和同步數據傳輸等應用中發揮著重要作用。了解和掌握74LS74的工作原理及應用,可以為設計和開發數字電子系統提供強有力的支持。通過合理利用74LS74,我們能夠設計出更為復雜和高效的數字電路,為各類電子產品的性能提升打下基礎。

九、74LS74 的電氣特性

9.1 電氣特性

了解74LS74的電氣特性對于設計電路至關重要。以下是其主要電氣特性參數:

輸入電流:當輸入高電平時,輸入電流通常在-0.2至-1.0毫安之間(最大值為±20μA),而在低電平狀態下,輸入電流幾乎為零。

輸出電壓:在邏輯高狀態時,輸出電壓通常接近于Vcc(5V),而在邏輯低狀態時,輸出電壓接近于0V。

開關時間:74LS74的開關時間(包括傳播延遲和上升/下降時間)約為15納秒,具體數值依賴于電路的負載條件和工作頻率。

功耗:74LS74的靜態功耗通常較低,典型值為20mW,最大功耗可達100mW。由于其低功耗特性,使其在低功耗應用中表現出色。

9.2 時序特性

74LS74的時序特性對于確保電路正常工作至關重要。其時序參數主要包括:

傳播延遲時間(tpd):表示輸入信號在時鐘邊沿到達輸出狀態所需的時間。通常為15-25納秒,具體取決于負載電流和電源電壓。

時鐘高電平持續時間(th):要求時鐘信號在高電平時應持續一定的時間,通常為10納秒。

數據保持時間(th):在時鐘上升沿到來之前,D輸入的數據必須保持有效的時間,通常為5納秒。

數據建立時間(ts):在時鐘信號的上升沿之前,D輸入的數據應被設置好的時間,通常為5納秒。

這些時序參數可以幫助工程師確保74LS74在高速應用中正確工作。

十、74LS74 的優缺點

10.1 優點

高速度:74LS74的快速響應能力使其適合于高頻應用,如高速計數器和數據鎖存器。

雙觸發器設計:集成兩個D觸發器節省了電路板空間,同時簡化了電路設計。

良好的兼容性:與TTL電路良好的兼容性使其在各種數字電路中廣泛應用。

簡單的接口:D型觸發器的輸入和輸出接口簡單易用,適合各種應用場景。

10.2 缺點

功耗:盡管74LS74的功耗較低,但在高頻應用中,功耗仍然是一個需要考慮的重要因素。

溫度敏感性:74LS74在高溫環境下可能會導致性能下降,因此在某些特定應用中需要進行溫度管理。

時序限制:在復雜的時序邏輯電路中,設計者需要非常注意時序參數,確保信號不會出現錯誤。

十一、74LS74 的設計考慮

在設計基于74LS74的電路時,有幾個關鍵因素需要考慮:

電源管理:確保電源穩定,避免電壓波動影響74LS74的工作。

時鐘信號:設計穩定且清晰的時鐘信號,以確保觸發器在正確的時鐘邊沿鎖存數據。

輸入輸出設計:合理設計D輸入和Q輸出,以防止短路或過載。

11.1 電路布局

在PCB設計中,74LS74的布局也需要特別關注,尤其是在高頻應用中:

減少走線長度:盡量減少信號線長度,以降低延遲和噪聲干擾。

合理的地線設計:為觸發器提供穩定的地線連接,避免地線噪聲對觸發器工作的影響。

電源旁路電容:在電源引腳上使用旁路電容,以減少電源波動對性能的影響。

11.2 邏輯分析與仿真

在設計完成后,使用邏輯分析儀或仿真軟件進行驗證,可以幫助確認電路在實際應用中的表現。這對于發現潛在問題和優化設計至關重要。

十二、74LS74 的替代品

在現代電子設計中,可能會遇到需要使用74LS74的替代品。這些替代品包括:

74HC74:更高的速度和更廣泛的電源電壓適用范圍,更適合現代CMOS設計。

74HCT74:TTL兼容性更強,適合多種邏輯電路的應用。

在選擇替代品時,需要綜合考慮電路的性能要求和兼容性。

十三、74LS74 在實際應用中的案例

13.1 計數器設計案例

在一個簡單的二進制計數器設計中,可以使用兩個74LS74觸發器構成一個4位二進制計數器。在此設計中,時鐘信號連接至每個D觸發器的CLK輸入,而D輸入則連接至Q'輸出,以形成反饋回路。這種設計確保每個觸發器在時鐘邊沿時對輸入數據進行采樣,從而實現計數功能。

13.2 狀態機應用

在某些控制系統中,可以使用74LS74構建有限狀態機(FSM)。例如,在交通信號控制系統中,D觸發器可以用來表示不同的信號燈狀態(紅燈、綠燈、黃燈),并根據傳感器輸入和定時器生成的時鐘信號進行狀態轉換。

13.3 數據存儲應用

在數據傳輸系統中,74LS74可以用作數據鎖存器。通過時鐘信號的控制,系統可以在特定時刻鎖存輸入的數據,并在后續處理過程中保持數據不變,直到需要再次更新。

十四、總結與展望

74LS74 D型正邊觸發觸發器是現代數字電路中不可或缺的基本組件。憑借其高速性能、低功耗特點以及廣泛的應用范圍,它在許多電子設備中發揮著重要作用。隨著技術的發展,未來可能會出現更高性能的觸發器,以滿足更復雜電路設計的需求。

通過對74LS74的深入了解,設計者能夠更有效地利用這一組件進行電路設計,實現更高效、更可靠的數字系統。掌握74LS74的使用與設計原則,將有助于工程師在日益復雜的電子設計中做出明智的決策。

產品分類

產品分類

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)